- 실리콘 포토닉스, AI와 HPC의 핵심 기술로 부상. 대역폭, 전송 거리, 전력 효율 면에서 기존 전기신호 통신 방식의 한계를 뛰어넘고 있음

- CPO(Co-packaged Optics)는 실리콘 포토닉스 기술을 기반으로 발전하고 있으며, 차세대 고급 반도체 패키징 기술로 주목받고 있음. GPU, CPU, 스위치에 광 기술을 직접 통합하여 비트 당 소비전력을 5피코줄(pJ) 이하로 낮출 수 있는 핵심 아키텍쳐

- 구글, 엔비디아, TSMC, AMD, 브로드컴 등 주요 기업들이 AI 인프라 핵심 전략에 실리콘 포토닉스를 적극 통합하고 있음

- AI 시대에 실리콘 포토닉스는 선택이 아닌 필수

실리콘 포토닉스가 기존 전기신호 통신 방식의 대역폭, 거리, 전력 효율의 한계를 돌파하며 AI 및 HPC(고성능 컴퓨팅)의 핵심 기술로 자리잡고 있다. 실리콘 포토닉스는 빛(광신호)을 이용해 데이터를 빠르고 효율적으로 전송하는 기술로, 기존 전자회로에 광 부품을 실리콘 위에 통합한 것이다. 공동 패키지형 광학인 CPO(Co-packaged optics)는 실리콘 포토닉스를 기반으로 GPU, CPU, 스위치에 광학을 직접 통합하는 차세대 패키징 아키텍처로, 더 높은 대역폭과 전력 효율을 제공한다.

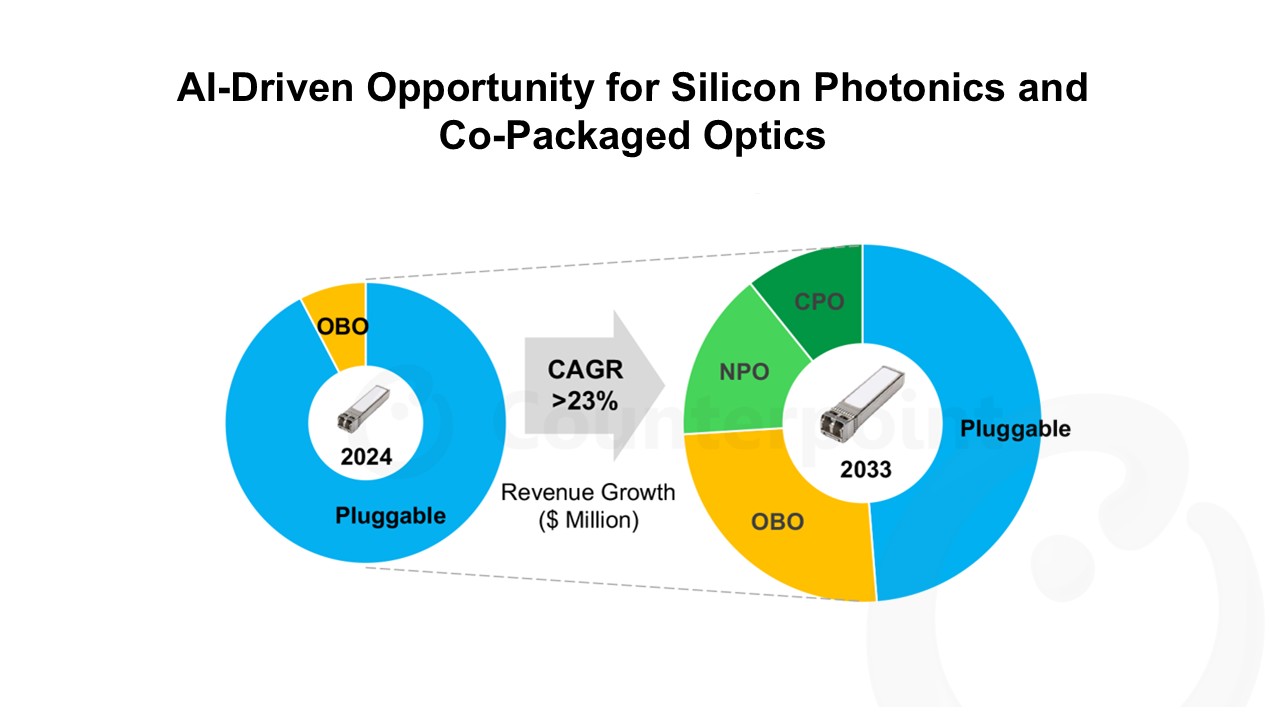

카운터포인트리서치(이하 “카운터포인트”)는 2030년까지 실리콘 포토닉스 관련 시장이 약 60억 달러 규모에 이를 것으로 전망했다. 엔비디아는 2025년 3월 GTC(GPU Technology Conference)에서 CPO가 적용된 스펙트럼-X 포토닉스를 발표했으며, 2026년 하반기 양산을 시작할 예정이다. 브로드컴 또한 2025년 6월 세계 최초의 102.4Tbps 이더넷 스위치 칩셋 ‘토마호크 6’ 출하를 개시하며 CPO 기술을 본격 상용화했다.

AI 기반 실리콘 포토닉스 및 CPO 시장 성장 전망

구글, 엔비디아, TSMC, AMD, 브로드컴 등 글로벌 선도 기업들은 AI 인프라 전략의 핵심 축으로 실리콘 포토닉스를 채택하고 있으며, TSMC의 쿠페(COUPE) 플랫폼은 첨단 로직(N7 이상)과 성숙 포토닉스(65nm SOI)를 결합해 224Gb/s 인터커넥트와 확장 가능한 WDM 솔루션을 지원한다.

CPO는 차세대 고급 반도체 패키징(ASP) 기술로 주목받으며, 비트당 5pJ 이하의 초저전력 데이터 전송을 가능하게 하는 핵심 아키텍처로 평가받고 있다. 다만, 업계는 열 관리, 패키징 통합, 표준화 측면에서의 과제를 해결해야 할 것이다. 그럼에도 불구하고 업계의 공통된 합의는 AI 시대에 실리콘 포토닉스는 선택이 아닌 필수라는 점이다.

수출 바우처 상담 문의

(카운터포인트 담당: 장한솔 hansol.jang@counterpointresearch.com)

카운터포인트리서치는 기술 생태계 전반에 걸쳐 시장 데이터, 인사이트, 리포트 및 컨설팅 서비스를 제공하는 글로벌 산업 및 시장 조사 기관입니다. 반도체 제조사, 부품 공급업체, 소프트웨어 및 애플리케이션 개발자부터 통신 서비스 제공업체, 유통 채널, 투자자에 이르기까지 공급망 전반에 걸친 다양한 글로벌 고객에게 자문을 제공합니다.

[카운터포인트리서치]

경험이 풍부한 당사의 애널리스트 팀은 전 세계 주요 혁신 허브, 제조 클러스터, 주요 상업 중심지에 위치한 글로벌 오피스를 통해 고객을 지원하고 있습니다. 기업 내 최고경영진(C-suite)부터 전략, 시장 인텔리전스, 공급망, 연구개발(R&D), 제품 관리, 마케팅, 영업 등 다양한 부서와 지속적으로 소통하고 있습니다.

카운터포인트 주요 연구 분야

: 인공지능(AI), 자동차, 클라우드, 커넥티비티, 소비자 가전, 디스플레이, eSIM, IoT(사물인터넷), 위치 기반 플랫폼, 거시경제, 제조, 네트워크 및 인프라, 반도체, 스마트폰 및 웨어러블 기기 등 공개된 시장 데이터, 인사이트 및 리포트를 확인하고, 애널리스트와의 소통을 원하시면 카운터포인트 라이브러리를 방문해 주세요.